Суперскаларна архитектура: как работи и защо ускорява процесорите

Научете как суперскаларната архитектура увеличава производителността чрез паралелно изпълнение на множество инструкции за такт, оптимизиран диспетчер и дублирани функционални единици.

Свръхвисокочестотният дизайн на процесора използва форма на паралелни изчисления, наречена паралелизъм на ниво инструкции, в един процесор, която позволява извършването на повече работа при една и съща тактова честота. Това означава, че процесорът може да изпълни повече от една инструкция в рамките на един тактов цикъл, като изпраща няколко инструкции едновременно към дублиращи се функционални единици. Всяко функционално звено е ресурс за изпълнение в ядрото на процесора — например аритметичен логически блок (ALU), блок с плаваща запетая (FPU), множител или специализирана SIMD единица.

Повечето суперскаларни процесори също са конвейерни, но е възможно да съществуват и неконвейерни суперскаларни дизайни или конвейерни несуперскаларни процесори. Комбинацията от супeрскаларност и конвейеризация увеличава пропусквателната способност, но и усложнява контрола и хардуерната логика.

Суперскаларната техника се подпомага от няколко ключови характеристики в ядрото:

- Инструкциите са подредени в поток, който може да бъде чел (fetch) с висока честота.

- Хардуерът може да разпознава зависимости между инструкциите и да предотвратява конфликтите за данни.

- Ядрото може да прочита и декодира няколко инструкции в един тактов цикъл.

Разликата между скаларни, векторни и суперскаларни подходи е следната:

- Скаларна инструкция обработва един или няколко елемента от данни (обикновено един резултат).

- Векторна инструкция (SIMD) обработва много елементи от данни с една инструкция.

- Суперскаларният процесор комбинира скаларни инструкции с множество функционални единици, така че няколко инструкции — всяка обработваща собствен елемент от данни — да се изпълняват едновременно.

В суперскаларния процесор специален модул — диспечер на инструкции — чете инструкции от паметта, анализира ролите им и решава кои от тях могат да се изпълняват паралелно, като ги изпраща към наличните функционални единици. За по-висока ефективност диспечерът трябва да запълва изпълнителните звена възможно най-постоянно.

Практически техники и хардуерни механизми, които позволяват това:

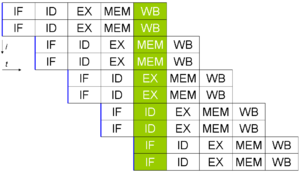

- Конвейеризация (pipelining) — разбиване на изпълнението на инструкции на етапи (fetch, decode, issue, execute, writeback, retire), което позволява едновременно обработване на множество инструкции в различни фази.

- Динамично (out-of-order) изпълнение — инструкции могат да се изпълняват извън програмния ред, ако няма зависимости, а техните резултати се запазват и връщат в архитектурния ред при приключване (retire). Това увеличава използването на единиците за изпълнение.

- Регистрово преименуване — премахва ложните зависимости (WAR, WAW) чрез картографиране на архитектурни регистри към вътрешни физически регистри.

- Резервационни станции и алгоритми като Tomasulo — управляват изчакване на операнди и издаване на инструкции към свободните функционални звена.

- Резервационни буфери и Reorder Buffer (ROB) — позволяват безопасно спекулативно изпълнение и коректно възстановяване при грешки или неправилно прогнозиран скок.

- Предсказване на клонове (branch prediction) — редуцира загубите от често срещани контролни прекъсвания в потока на инструкции; точното предсказване е критично за запълване на конвейера и изпълнителните звена.

Типичен животен цикъл на инструкция в суперскаларен процесор включва: fetch (четене), decode (декодиране), issue (издаване към функционалните звена), execute (изпълнение), writeback (записване на резултата) и retire (потвърждаване в архитектурния ред). Хардуерът трябва да управлява зависимости между инструкции — RAW (read after write), WAR (write after read) и WAW (write after write) — за да избегне грешни резултати.

Ограничения и предизвикателства:

- Зависимости между инструкциите и случайни достъпи до памет ограничават достъпната ширина на паралелизъм (ILP). Съществува закон на намаляваща възвръщаемост — с нарастване на броя на паралелните декодирани инструкции, ползата често намалява.

- Предсказването на клонове и кеш и/или латентността на паметта играят голяма роля — пропуски от кеш могат да „изпразнят“ конвейера и да намалят ползата от суперскаларността.

- Хардуерната сложност, площ и консумация на енергия растат бързо с увеличаване на броя функционални единици, ширината на декодиране и механизмите за динамично издаване.

- Проектирането на диспечера и средствата за управление на зависимости са сложни и скъпи за верификация и производство.

Сравнение с други подходи:

- VLIW (Very Long Instruction Word) — прехвърля отговорността за извличане на паралелизма към компилатора чрез пакети инструкции, които хардуерът изпълнява без динамична проверка за зависимости. По-прост хардуер, но по-голяма зависимост от качеството на компилатора и проблеми със съвместимостта/оптимизацията при различни архитектури.

- SIMD — добре пасва за данни-паралелни задачи (медии, ML, графика), докато суперскаларността увеличава общия ILP в порядъка на потока от инструкции.

- SMT / Hyper-Threading — многопоточност в един физически ядро (напр. Intel Hyper-Threading) може да запълни празнини в изпълнението, когато един поток е блокиран; комбинира се често със суперскаларност.

- Многоядрена архитектура — за някои натоварвания мащабирането се решава чрез повече ядра, а не чрез по-широк суперскаларен дизайн, поради сложността и енергийния разход при последния.

Исторически и практически бележки:

- От около 2008 г. повечето CPU с общо предназначение са суперскаларни; типичните конфигурации за десктоп/мобилни ядра често имат няколко ALU, 1–2 FPU и допълнителни SIMD блокове. Високопроизводителните процесори могат да имат по-широки декодери и повече изпълнителни единици (някои сървърни/специализирани ядра декодират 4–6+ инструкции за такт).

- Ако диспечерът не успее да поддържа занятостта на всички функционални звена (поради зависимости, грешки в предсказването на клонове или пропуски от кеш), производителността ще спадне спрямо теоретичния максимум.

- Много известни архитектури (x86, ARM) използват суперскаларни техники, често в комбинация с out-of-order изпълнение, предсказване на клонове и регистрово преименуване.

Заключение: суперскаларната архитектура ускорява процесорите, защото позволява едновременна обработка на множество независими инструкции чрез паралелни функционални единици и сложни механизми за динамично планиране и управление на зависимости. Тя носи значителни печалби в производителността за общи натоварвания, но изисква допълнителни хардуерни ресурси и сложна логика, което налага компромиси в консумацията на енергия, площта и цената на чипа.

Бележка: за по-дълбоко разбиране търсете термини като "out-of-order execution", "Tomasulo algorithm", "reorder buffer", "register renaming", "branch predictor" и "instruction-level parallelism".

Процесорна платка на паралелен компютър CRAY T3e с четири суперскаларни процесора Alpha

Обикновен суперскаларен конвейер. Чрез извличане и изпращане на две инструкции едновременно могат да бъдат изпълнени максимум две инструкции на цикъл.

Ограничения

Подобряването на производителността при проектирането на суперскаларни процесори е ограничено от две неща:

- Нивото на вграден паралелизъм в списъка с инструкции

- Сложността и времевите разходи на диспечера и проверката на зависимостта на данните.

Дори при безкрайно бърза проверка на зависимостите в нормален суперскаларен процесор, ако самият списък с инструкции има много зависимости, това също ще ограничи възможното подобрение на производителността, така че количеството вграден паралелизъм в кода е друго ограничение.

Независимо от това колко висока е скоростта на диспечера, съществува практическо ограничение за това колко инструкции могат да бъдат изпратени едновременно. Макар че хардуерният напредък ще позволи повече функционални единици (например ALU) на едно процесорно ядро, проблемът с проверката на зависимостите на инструкциите се увеличава до такава степен, че постижимата граница на суперскаларното диспечиране е малко по-малка. -- Вероятно от порядъка на пет до шест едновременно изпратени инструкции.

Алтернативи

- Едновременна многонишковост: често съкращавана като SMT, е техника за подобряване на общата скорост на суперскаларните процесори. SMT позволява множество независими нишки на изпълнение, за да се използват по-добре ресурсите, налични в един съвременен суперскаларен процесор.

- Многоядрени процесори: суперскаларните процесори се различават от многоядрените процесори по това, че множеството излишни функционални единици не са цели процесори. Един суперскаларен процесор се състои от усъвършенствани функционални единици, като ALU, умножител на цели числа, шифър на цели числа, блок за плаваща запетая (FPU) и др. Може да има няколко версии на всяка функционална единица, за да се даде възможност за паралелно изпълнение на много инструкции. Това се различава от многоядрените процесори, които обработват едновременно инструкции от няколко нишки, по една нишка на ядро.

- Процесори с конвейерно свързване: суперскаларните процесори също се различават от процесорите с конвейерно свързване, при които множество инструкции могат да бъдат едновременно на различни етапи на изпълнение.

Различните алтернативни техники не се изключват взаимно - те могат да се комбинират (и често се комбинират) в един процесор, така че е възможно да се проектира многоядрен процесор, в който всяко ядро е независим процесор с множество паралелни суперскаларни конвейери. Някои многоядрени процесори включват и векторни възможности.

Свързани страници

- Паралелни изчисления

- Паралелизъм на ниво инструкция

- Едновременна многонишковост (SMT)

- Многоядрени процесори

Въпроси и отговори

В: Какво представлява свръхскаларната технология?

О: Свръхскаларната технология е форма на основни паралелни изчисления, която позволява обработката на повече от една инструкция за всеки тактов цикъл чрез използване на няколко единици за изпълнение едновременно.

В: Как работи суперскаларната технология?

О: Свръхскаларната технология включва инструкции, които постъпват в процесора в определен ред, търсене на зависимости от данни по време на работа и зареждане на повече от една инструкция за всеки тактов цикъл.

В: Каква е разликата между скаларните и векторните процесори?

О: При скаларния процесор инструкциите обикновено работят с един или два елемента данни едновременно, докато при векторния процесор инструкциите обикновено работят с много елементи данни едновременно. Свръхскаларният процесор е комбинация от двете, тъй като всяка инструкция обработва един елемент от данни, но повече от една инструкция се изпълнява едновременно, така че процесорът обработва много елементи от данни наведнъж.

Въпрос: Каква роля играе точният диспечер на инструкции в суперскаларния процесор?

О: Точният диспечер на инструкциите е много важен за суперскаларния процесор, тъй като гарантира, че звената за изпълнение са винаги заети с работа, която вероятно ще бъде необходима. Ако диспечерът на инструкциите не е точен, може да се наложи част от работата да бъде изхвърлена, което би го направило не по-бърз от скаларен процесор.

Въпрос: През коя година всички нормални процесори станаха суперскаларни?

О: През 2008 г. всички нормални процесори станаха суперскалери.

В: Колко ALU, FPU и SIMD единици може да има един нормален процесор?

О: В един нормален процесор може да има до 4 ALU, 2 FPU и 2 SIMD единици.

обискирам